Giới thiệu chung về transistor trường FET, Mai Hoàng Nam

Mai Hoàng Nam - 20100471 Nhiệt lạnh 1 - K55 - Đại Học Bách Khoa Hà Nội

GIỚI THIỆU CHUNG VỀ TRANSISTOR TRƯỜNG FET

Mục lục

|

FET[sửa]

1.1 Nguyên lý hoạt động cơ bản[sửa]

Nguyên lý hoạt động cơ bản của tranzito trường là dòng điện đi qua một môi trường bán dẫn có tiết diện dẫn điện thay đổi dưới tác dụng của điện trường vuông góc với lớp bán dẫn đó. Khi thay đổi cường độ điện trường sẽ làm thay đổi điện trở của lớp bán dẫn và do đó làm thay đổi dòng điện đi qua nó. Lớp bán dẫn này được gọi là kênh dẫn điện.

1.2 Phân loại[sửa]

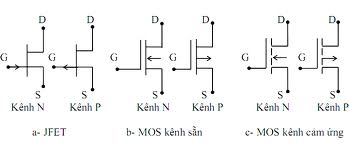

Tranzito trường có hai loại chính là:

- Tranzito trường điều khiển bằng tiếp xúc P-N (hay gọi là tranzito trường mối nối): Junction field- effect transistor - viết tắt là JFET.

- Tranzito có cực cửa cách điện: MOSFET

Chia làm 2 loại là MOSFET kênh sẵn và MOSFET kênh cảm ứng. Mỗi loại FET lại được phân chia thành loại kênh N và loại kênh P.

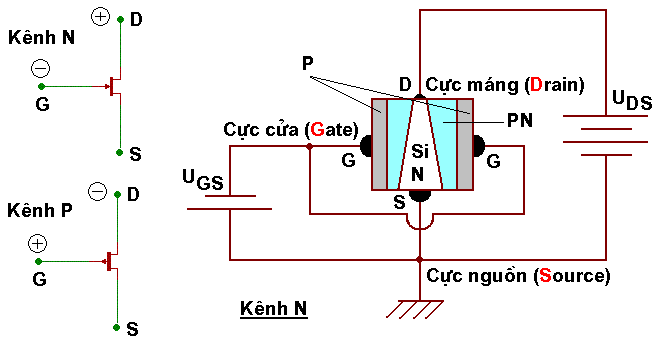

1.3 Cấu tạo chung[sửa]

Tranzito trường có ba chân cực là cực Nguồn ký hiệu là chữ S (source); cực Cửa ký hiệu là hữ G (gate); cực Máng ký hiệu là chữ D (drain). Cực nguồn (S): cực nguồn mà qua đó các hạt dẫn đa số đi vào kênh và tạo ra dòng điện nguồn IS. Cực máng (D): là cực mà ở đó các hạt dẫn đa số rời khỏi kênh. Cực cửa (G): là cực điều khiển dòng điện chạy qua kênh.

1.4 Ưu nhược điểm của Transistor trường[sửa]

Ưu điểm

+ Dòng điện qua tranzito chỉ do một loại hạt dẫn đa số tạo nên. Do vậy FET là loại cấu kiện đơn cực (unipolar device).

+ FET có trở kháng vào rất cao.

+ Tiếng ồn trong FET ít hơn nhiều so với tranzito lưỡng cực.

+ Nó không bù điện áp tại dòng ID = 0 và do đó nó là cái ngắt điện tốt.

+ Có độ ổn định về nhiệt cao.

+ Tần số làm việc cao.

Nhược điểm:

Nhược điểm chính của FET là hệ số khuếch đại thấp hơn nhiều so với tranzito lưỡng cực.

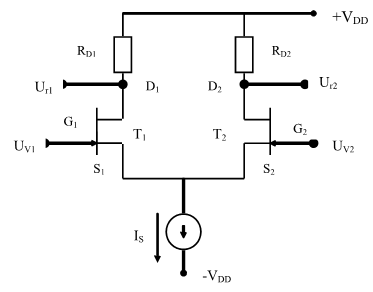

1.5 Tầng khuếch đại vi sai dùng FET[sửa]

Về nguyên lý hoạt động của mạch khuếch đại vi sai không có gì khác với mạch dùng tranzito lưỡng cực, chỉ có trở kháng vào của mạch dùng FET thì lớn hơn nhiều (có thể tới hàng trăn lần cao hơn so với dùng BJT).

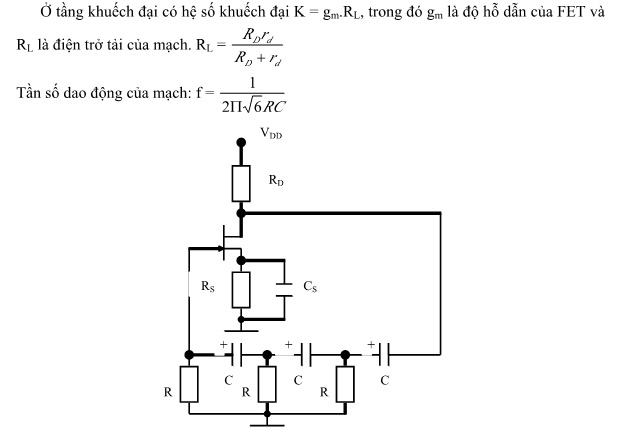

1.6 Mạch phát sóng RC dùng FET[sửa]

Ở tầng khuếch đại có hệ số khuếch đại K=gm.RL, trong đó gm là độ hỗ dẫn của FET và RL là điện trở tải của mạch.

Mạch tạo dao động RC cho dao động có tần số đủ thấp. Trong khối khuếch, tín hiệu ra ngược pha với tín hiệu vào (FET mắc Nguồn chung) nên mạch hồi tiếp RC phụ thuộc tần số phải dịch pha tín hiệu 1800 ở tần số phát sóng.

JFET[sửa]

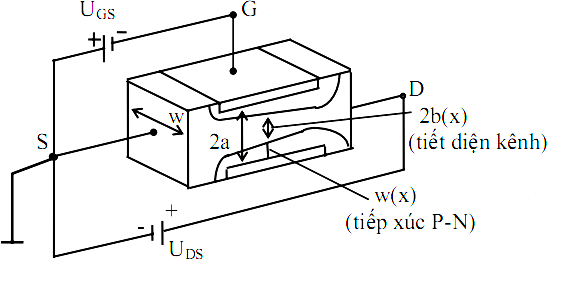

2.1 Cấu tạo và nguyên lý làm việc[sửa]

2.1.1 Cấu tạo[sửa]

2.1.2 Nguyên lý hoạt động[sửa]

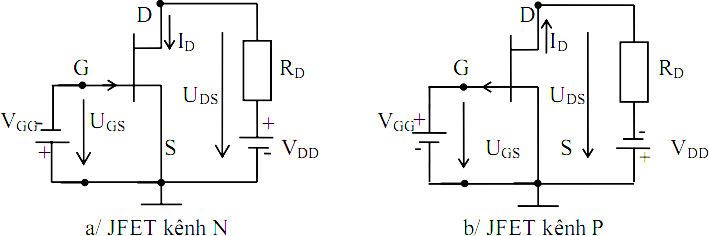

- Về cơ bản nguyên lý hoạt động của 2 loại Jfet tương đối giống nhau, chỉ khác nhau về chiều dòng điện

- Ở chế độ khuếch đại, ta phải cấp nguồn UGS để 2 tiếp xúc P-N phân cực ngược. Nguồn UDS làm cho các hạt dẫn đa số chuyển động từ cực nguồn S về cực máng D => tạo dòng ID trong mạch cực máng

Ta xét JFET kênh N:

- Điện áp VGG đặt tới cực G và S để phân cực ngược cho tiếp giáp P-N. Điện áp VDD đặt tới D và S để tạo ra dòng điện chay trong kênh dẫn.

- Điện áp phân cực ngược đặt tới G và S làm cho vùng nghèo dọc theo tiếp giáp P-N được mở rộng ra chủ yếu về phía kênh dẫn, điều này làm kênh hẹp lại hơn do đó điện trở kênh dẫn tăng lên và dòng qua kênh dẫn giảm đi. Với cách phân cực trên thì điện áp phân cực giữa G và D lớn hơn điện áp phân cực ngược giữa G và S làm cho vùng nghèo mở rộng không đều

2.1.3 Đặc tuyến của JFET[sửa]

• Đặc tuyến ra:

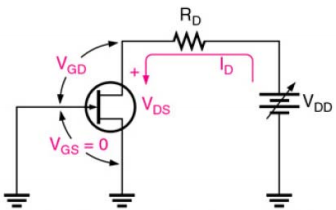

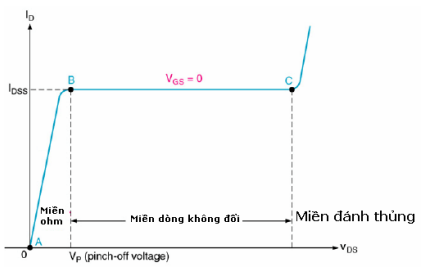

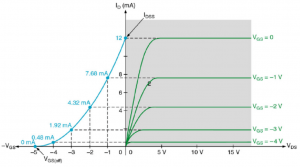

Xét trường hợp JFET phân cực với điện áp VGG=0

- Tăng dần VDD thì VDS tăng và ID tăng tuyến tính theo. Khi tăng VDD thì vùng nghèo có xu hướng rộng ra, tuy nhiên khi VDD chưa đủ lớn thì bề rộng của vùng nghèo chưa đủ rộng để gây ảnh hưởng tới ID => ID & VDS có mối quan hệ tuyến tính khi VDD đủ nhỏ. Mối quan hệ này thể hiện ở đặc tuyến ra A → B ( Miền OHM).

- VDD đủ lớn, khi đó VDS đủ lớn, lúc này bề rộng vùng nghèo bắt đầu gây ảnh hưởng dòng ID. Nó kiềm hãm sự tăng của dòng ID trước sự tăng của VDS. Mối quan hệ này thể hiện ở đặc tuyến ra B → C (Miền không đổi)

- VDD tiếp tục tăng đến giá trị đủ lớn để đánh thủng tiếp giáp P-N thì ID tăng đột ngột theo VDS, miền này gọi là miền đánh thủng; JFET làm việc ở chế độ này sẽ bị hỏng

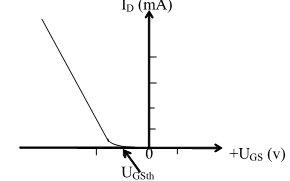

• Đặc tuyến truyền đạt:

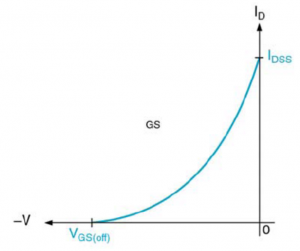

Ta thấy VGS(0 → VGS off) điều khiển dòng ID. Với JFET kênh N VGS off < 0, JFET kênh P VGS off > 0. Đồ thị thể hiện mối quan hệ VGS và ID là đặc tuyến truyền đạt, có dạng:

Đường cong này chính là đặc tuyến truyền đạt của JFET kênh N, cho ta biết giới hạn hoạt động của JFET.

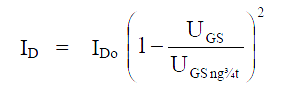

FET được xếp vào các linh kiện tuân theo luật bình phương

2.2 Các cách mách của JFET trong sơ đồ mạch[sửa]

Như các tranzito lưỡng cực, tranzito trường cũng có 3 cách mắc trong các sơ đồ mạch khuếch đại là: sơ đồ mắc cực nguồn chung, sơ đồ mắc cực máng chung, sơ đồ mắc cực cửa chung.

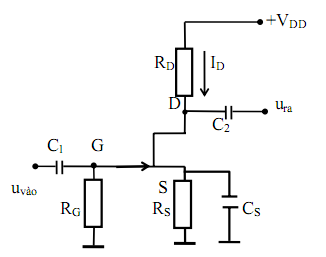

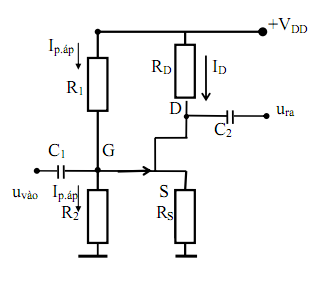

2.2.1 Sơ đồ cực nguồn chung:[sửa]

Nguồn cung cấp một chiều VDD, điện trở định thiên RG, tải RD. Sơ đồ mắc cực nguồn chung giống như sơ đồ mắc cực phát chung đối với các tranzito lưỡng cực, có điểm khác là dòng vào IG thực tế bằng 0 và trở kháng vào rất lớn.

Đặc điểm của sơ đồ cực nguồn chung:

- Tín hiệu vào và tín hiệu ra ngược pha nhau.

- Trở kháng vào rất lớn Z vào = RGS ≈ ∞

- Trở kháng ra Zra = RD // rd

- Hệ số khuếch đại điện áp μ ≈ S rd > 1

Đối với tranzito JFET kênh N thì hệ số khuếch đại điện áp khoảng từ 150 lần đến 300 lần, còn đối với tranzito JFET kênh loại P thì hệ số khuếch đại chỉ bằng một nửa là khoảng từ 75 lần đến 150 lần.

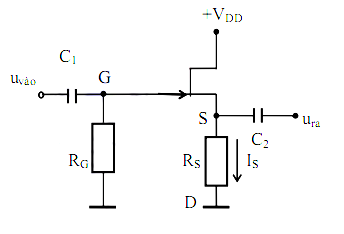

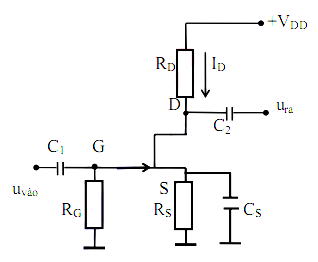

2.2.2 Sơ đồ mắc cực máng chung:[sửa]

Sơ đồ mắc cực máng chung giống như sơ đồ mắc cực góp chung của tranzito lưỡng cực. Tải RS được đấu ở mạch cực nguồn và sơ đồ còn được gọi là mạch lặp cực nguồn.

Đặc điểm của sơ đồ này có:

- Tín hiệu vào và tín hiệu ra đồng pha nhau.

- Trở kháng vào rất lớn

Zvào = RGD = ∞

- Trở kháng ra rất nhỏ Zra = RS

- Hệ số khuếch đại điện áp μ < 1

Sơ đồ cực máng chung được dùng rộng rãi hơn, cơ bản là do nó giảm được điện dung vào của mạch, đồng thời có trở kháng vào rất lớn. Sơ đồ này thường được dùng để phối hợp trở kháng giữa các mạch.

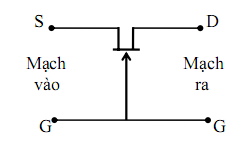

2.2.3 Sơ đồ mắc cực cửa chung:[sửa]

Sơ đồ này theo nguyên tắc không được sử dụng do có trở kháng vào nhỏ, trở kháng ra lớn.

2.3 Phân cực cho JFET[sửa]

Giống như tranzito lưỡng cực, tranzito trường cũng có các cách phân cực như: phân cực cố đinh, phân cực phân áp và phân cực hồi tiếp.

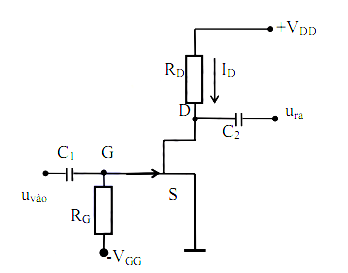

2.3.1 Phân cực cố định[sửa]

Trong cách phân cực này nguồn điện VGG được đặt vào cực cửa và mạch được gọi là phân cực cố định vì có UGS = -UGG có giá trị cố định.Như vậy, muốn xác định điểm làm việc Q thích hợp ta phải dùng 2 nguồn cung cấp. Đây là điều bất lợi của phương pháp phân cực này.

2.3.2 Phân cực phân áp[sửa]

Phương pháp này rất hữu hiệu cho tranzito lưỡng cực nhưng đối với JFET thì không tiện lợi khi sử dụng.

2.3.3 Phân áp tự cấp (còn gọi là tự phân cực)[sửa]

Đây là cách phân cực không giống như đối với BJT và nó là cách phân cực hữu hiệu nhất đối với JFET, trong cách phân cực này thì điện áp UGS = D-IRS.

2.4 Các tham số của FET ở chế độ tín hiệu nhỏ[sửa]

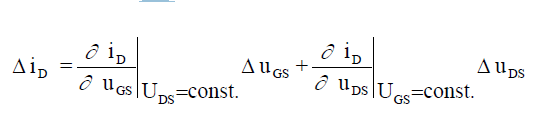

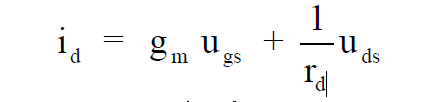

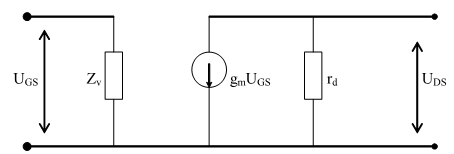

Các tham số của FET thường là: độ hỗ dẫn, trở kháng ra, trở kháng vào và hệ số khuếch đại. Sơ đồ mạch tương đương của Fet ở chế độ tín hiệu nhỏ cũng giống như ở transistor lưỡng cực. ở chế độ này dòng điện cực máng Id là một hàm của điện áp trên cực cửa UGS và điện áp trên cực máng UDS, ta có:

ID = f(UGS,, UDS )

Khi cả hai điện áp trên cực cửa và cực máng đều biến đổi thì dòng điện thì dòng điện cực máng sẽ thay đổi theo

Trong chế độ tín hiệu nhỏ các đại lượng ∆iD = id ; ∆uGS = ugs ; ∆uDS = uds như vậy công thức trên được viết :

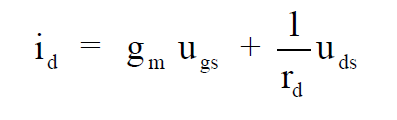

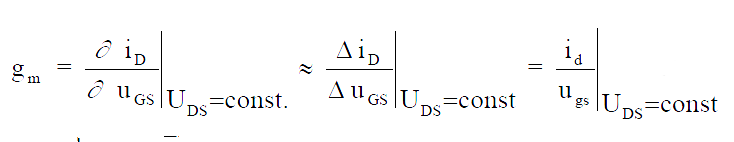

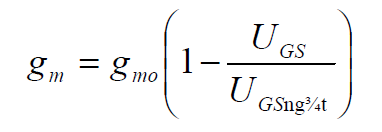

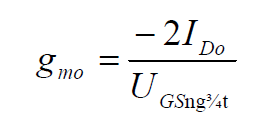

2.4.1 Độ hỗ dẫn ( kí hiệu là gm)[sửa]

Độ hỗ dẫn của FET biểu thị khả năng điều khiển của điện áp cực cửa UGS lên dòng điện xoay chiều cực máng ID . Giá trị hỗ dẫn nằm trong khoảng S = 3 : 20 mA/V.

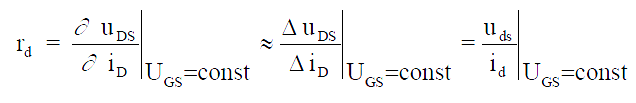

2.4.2 Điện trở ra hay còn gọi là điện trở máng( rd)[sửa]

Điện trở máng biểu thị sự ảnh hưởng của điện áp cực máng UDS và dòng điện cực máng ID ta có công thứC:

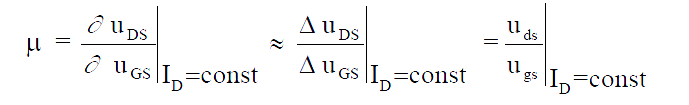

2.4.3 Hệ số khuếch đại điện áp µ[sửa]

Hệ số khuếch đại điện áp trên cực cửa tác động lên dòng điện cực máng mạnh hơn so với điện áp trên cực máng. Ta có công thức:

So sánh các công thức tính độ hổ dẫn gm , điện trở máng rd à hệ số khuếch đại điện áp µ ta có công thức:

Hệ số khuếch đại có giá trị khoảng từ vài chục đến vài trăm lần.

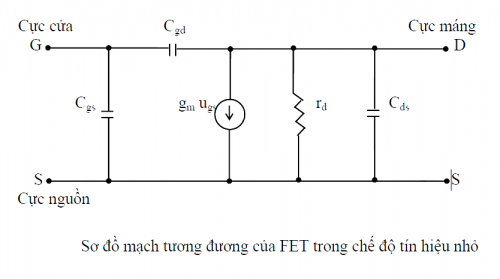

2.5 Sơ đồ tương đương của FET trong chế độ tín hiệu nhỏ[sửa]

Tụ điện CGS là điện dung kí sinh của FET khi transistor làm việc ở tần số thấp thì chúng không gây ảnh hưởng gì cho mạch, nhưng khi tần số cao chúng có thể gây ngắn mạch giữa các chân cực của transistor. Vì tiếp xúc P-N của cực cửa phân cực ngược nên các điện trở giữa cực cửa - cực nguồn rGS , và cực cửa - cực máng rDG do đó hai điện trở này được bỏ qua.

Ta có:

Và

Ta tính được:

Trong đó gmo là giá trị độ hổ dẫn khi UGS = 0 và được xác định

Vì IDO và UGSngắt ngược pha nhau nên g mo luôn dương.

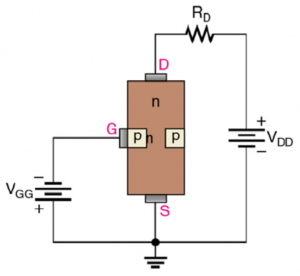

3. Tranzito trường loại cực cửa cách ly (IGFET)[sửa]

Đây là loại tranzito trường có cực cửa cách điện với kênh dẫn điện bằng một lớp cách điện mỏng. Lớp cách điện thường dùng là chất oxit nên ta thường gọi tắt là tranzito trường loại MOS. Tên gọi MOS được viết tắt từ ba từ tiếng Anh là: Metal - Oxide - Semiconductor.

Tranzito trường MOS có hai loại: tranzito MOSFET có kênh sẵn và tranzito MOSFET kênh cảm ứng. Trong mỗi loại MOSFET này lại có hai loại là kênh dẫn loại P và kênh loại N.

3.1 Cấu tạo và nguyên lý hoạt động của MOSFET kênh sẵn[sửa]

3.1.1 Cấu tạo:[sửa]

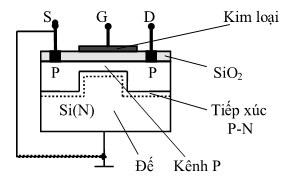

Tranzito trường MOSFET kênh sẵn còn gọi là MOSFET-chế độ nghèo (Depletion-Mode) MOSFET viết tắt là DMOSFET. Tranzito trường loại MOS có kênh sẵn là loại tranzito mà khi chế tạo người ta đã chế tạo sẵn kênh dẫn.

3.1.2 Nguyên lý hoạt động[sửa]

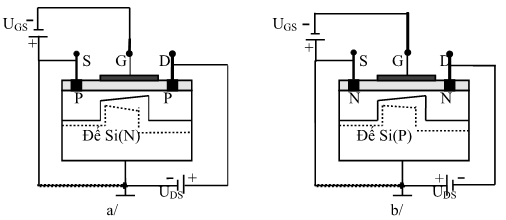

Tranzito loại MOSFET kênh sẵn có hai loại là kênh loại P và kênh loại N.Khi tranzito làm việc, thông thường cực nguồn S được nối với đế và nối đất nên US = 0.Các điện áp đặt vào các chân cực cửa G và cực máng D là so với chân cực S. Nguyên tắc cung cấp nguồn điện cho các chân cực sao cho hạt dẫn đa số chạy từ cực nguồn S qua kênh về cực máng D để tạo nên dòng điện ID trong mạch cực máng. Còn điện áp đặt trên cực cửa có chiều sao cho MOSFET làm việc ở chế độ giàu hạt dẫn hoặc ở chế độ nghèo hạt dẫn

Nguyên lý làm việc của hai loại tranzito kênh P và kênh N giống nhau chỉ có cực tính của nguồn điện cung cấp cho các chân cực là trái dấu nhau.

MOSFET kênh sẵn loại P MOSFET kênh sẵn loại N

a-

MOSFET

kênh

sẵn

loại

P.

b- MOSFET kênh sẵn loại N

3.2 Cấu tạo và nguyên lý hoạt động của MOSFET kênh cảm ứng[sửa]

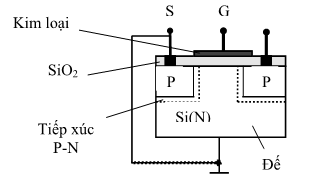

3.2.1 Cấu tạo:[sửa]

Tranzito trường loại MOS kênh cảm ứng còn gọi là MOSFET chế độ giàu (Enhancement-Mode MOSFET vi ết tắt là E-MOSFET). Khi chế tạo MOSFET kênh cảm ứng người ta không chế tạo kênh dẫn. Do công nghệ chế tạo đơn giản nên MOSFET kênh cảm ứng được sản xuất và sử dụng nhiều hơn.

3.2.2 Nguyên lý hoạt động[sửa]

Nguyên lý làm việc của loại kênh P và kênh N giống hệt nhau chỉ khác nhau về cực tính của nguồn cung cấp đặt lên các chân cực. Trước tiên, nối cực nguồn S với đế và nối đất, sau đó cấp điện áp giữa cực cửa và cực nguồn để tạo kênh dẫn.

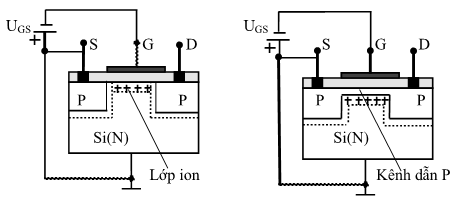

Tạo kênh dẫn và khả năng điều khiển của tranzito:

Ta trình bày nguyên lý hoạt động của MOSFET kênh cảm ứng loại P.

Theo nguyên tắc cấp nguồn điện cho các chân cực, ta cấp nguồn điện UGS < 0 để tạo kênh, còn UDS < 0 để tác động cho các lỗ trống chuyển động từ cực nguồn về cực máng tạo nên dòng điện ID.

Khi ta đặt một điện áp lên cực cửa âm hơn so với cực nguồn (UGS < 0) đến một giá trị gọi là điện áp ngưỡng (ký hiệu là UGSth) thì một số các lỗ trống được hút về tạo thành một lớp mỏng các lỗ trống trên bề mặt của lớp bán dẫn đế Si(N), nối liền cực nguồn S với cực máng D và kênh dẫn điện được hình thành.

Sự hình thành kênh dẫn của MOSFET loại P

Khi kênh đã xuất hiện, dưới tác dụng của điện trường cực máng các lỗ trống sẽ di chuyển

từ cực nguồn, qua kênh, về cực máng và tạo nên dòng điện trong tranzito ID

Tiếp tục cho UGS càng âm hơn, nghĩa là |UGS|>|UGSth|, thì số lỗ trống được hút về kênh càng nhiều, mật độ hạt dẫn trong kênh càng tăng lên, độ dẫn điện của kênh càng tăng dẫn đến cường độ dòng điện chạy qua kênh cũng tăng lên.

3.3 Các cách mắc của MOSFET trong sơ đồ mạch khuếch đại[sửa]

Giống như JFET, tranzito loại MOSFET cũng có 3 cách mắc cơ bản là cực nguồn chung, cực máng chung và cực cửa chung. Trong 3 cách mắc này thì cách mắc cực cửa chung không được sử dụng trên thực tế. Do vậy, thông thường ta sử dụng hai cách mắc nguồn chung và máng chung.

3.4 Phân cực cho MOSFET[sửa]

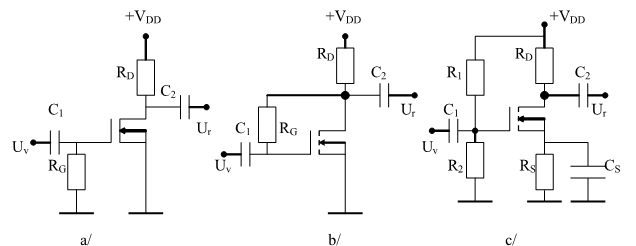

Cũng như BJT và JFET, thông thường có 3 cách phân cực cho MOSFET là: a/ phân cực cố định, b/ phân cực hồi tiếp và c/ phân cực phân áp.

Phân cực zero và ID = IDo. Đây là cách phân cực đơn giản nhất. Sơ đồ hình b là cách phân cực hồi tiếp cực máng cho MOSFET kênh cảm ứng. Do dòng IG = 0 nên URG = 0V và Ur = Uv . Sơ đồ hình c là mạch phân cực phân áp. Ở cách phân áp này có trở kháng vào Zv = R1//R2; UGS = UG – IDRS.

3.5 Sơ đồ mạch tương đương của MOSFET[sửa]

Trong sơ đồ, điện trở Zv rất lớn (Zv = RGS ≈ ∞) nên trong các sơ đồ mạch tương đương mạch vào gần như hở mạch. Điện trở rd là trở kháng ra và nó là điện trở của kênh đối với thành phần xoay chiều.

4. Một số ứng dụng của FET[sửa]

Trong kỹ thuật điện tử, tranzito trường được sử dụng gần giống như tranzito lưỡng cực. Tuy nhiên, do một số các ưu nhược điểm của FET so với BJT đã nói ở trên, đặc biệt là hệ số khuếch đại thấp, mà tranzito trường thường được sử dụng ở những mạch thể hiện được ưu thế của chúng. Đặc biệt trong việc tích hợp IC thì tranzito trường được ứng dụng rất hiệu quả vì cho phép tạo ra các IC có độ tích hợp rất cao (LSI và VLSI). FET được dùng khuyếch đại vi sai, phát sóng RC...