Cắt lớp trở kháng

Phần I. Mở đầu

Chụp cắt lớp vi tính hiện nay là phương tiện rất cần thiết cho chẩn đoán hình ảnh. Phương pháp chụp cắt lớp vi tính đã giúp cho các nhà lâm sàng và phẫu thuật nhận định một cách đầy đủ các tổn thương, từ đó có chỉ định, tiên lượng cuộc mổ, theo dõi điều trị một cách hợp lý nhất. Tuy nhiên một vấn đề là khi chụp cắt lớp điện toán thì bệnh nhân phải nhận một liều lượng phóng xạ có ảnh hưởng tới bệnh nhân. Ngày 27/4/2010, Cơ quan Năng lượng nguyên tử quốc tế (IAEA) cảnh báo việc trẻ em phải chịu lượng phóng xạ quá mức khi chụp cắt lớp (CT) có thể làm tăng nguy cơ mắc các bệnh ung thư. Một trong nhưng phương pháp khác để tạo ảnh cắt lớp là phương pháp cắt lớp trở kháng (Electrical impedance tomography (EIT)), với phương pháp này bệnh nhân không phải chịu một liều lượng phóng xạ nào và đây là một phương pháp ít gây ảnh hưởng nhất tới cơ thể.

Tuy vậy, trong tạo ảnh trở kháng, hình ảnh bị làm mờ bởi vì trong một vật dẫn khối đường đi của dòng điện là không tuyến tính và nói chung là không biết được chính xác. Mặc dù mục đích cơ bản của cắt lớp trở kháng là tái tạo một ảnh trở kháng từ một lát cắt của một vùng 3 chiều của cơ thể, nó cũng có thể được dùng để kiểm tra một cách chính xác hơn một vài thông số sinh lý học. Woo, Hua, và Webster (1992) đã trình bày một ví dụ về loại thiết bị kiểm tra trẻ sơ sinh ngạt thở đáng tin cậy hơn. Với kỹ thuật cắt lớp trở kháng, có thể tập trung vào việc thu thập các dữ liệu trở kháng chính xác hơn tới vùng phổi và vì vậy tránh được nhiễu gây ra bởi sự chuyển động của thành ngực.

Với tác dụng của phương pháp cắt lớp trở kháng dùng trong lâm sàng việc nghiên cứu chế tạo hệ thống cắt lớp trở kháng là điều cần thiết phục vụ cho ngành y học. Trong bước đầu của dự án là thu thập thông tin lưu trữ trên máy tính phục vụ cho việc xử lý tái tại hình ảnh ở bước tiếp theo. Do vậy công việc dùng lại ở mức thiết kế hệ thống thu thập dữ liệu cần thiết để tái tạo ảnh.

Phần II.Tổng quan về lý thuyết

2.1. Mô hình toán học của cắt lớp trở kháng

Mô hình toán học chủ yếu của cắt lớp trở kháng chủ yếu liên quan đến bài toán chuyển tiếp và bài toán ngược (forward and inverse problems)

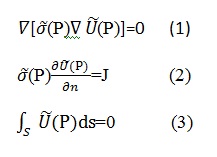

Trong bài toán chuyển tiếp, các biểu thức được hiệu chỉnh từ phương trình Maxwell trong dải tần số thấp:

Với U ̃(P) là điện áp

σ ̃(P) là độ dẫn nạp đặc trưng của B

Trong đó σ ̃(P) = σ(P) + jωε(P)

Các biểu thức (1),(2) và (3) ở trên là những phương trình toán học cơ bản trong cắt lớp trở kháng

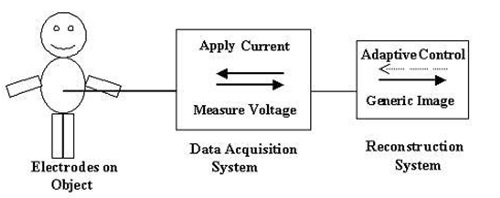

2.2. Mô hình hệ thống

Mô hình tổng quan của hệ thống cắt lớp trở kháng:

Hệ thống bao gồm 3 khối chính:

Thứ nhất là khối các điện cực được gắn vào đối tượng cần đo

Thứ hai là khối kích dòng vào đối tượng và thu thập các điện áp đo được

Thứ ba là khối khôi phục lại hình ảnh của vùng vừa đo

Hệ thống ban đầu chỉ là một hệ thống thu thập thông tin vì vậy chỉ quan tâm đến các phương pháp đo trở kháng mà chưa quan tâm đến lý thuyết khác liên quan đến việc tái tạo hình ảnh. Do vậy mà hệ thống chỉ có hai khối là khối thứ nhất và khối thứ hai,còn khối thứ ba sẽ được nhóm tiếp tục nghiên cứu để hoàn thiện hệ thống.

2.3. Các phương pháp đo

Trở kháng điện có thể được đo truyền thống bằng phương pháp hoàn toàn dòng điện hoặc bằng phương pháp điện từ. Thực tế phương pháp điên từ truyền thống đã có những phương pháp đo sau được sử dụng:

Phép đo điện của trở kháng gồm có:

Phương pháp lân cận (Neighboring Method): Vị trí đặt điện cực kích thích dòng là cố định và thực hiện đo điện áp ở các điểm khác nhau:

Ưu điểm:

-Vị trí dòng kích là cố định

-Số phép đo điện áp là ít hơn so với các phương pháp khác

Nhược điểm:

-Một vài giả định của phương pháp này là chưa đúng (theo nghiên cứu sau của Kauppinen, Hyttinen, và Malmivuo (2006))

Phương pháp Cross: Điện cực kích dòng có sự thay đổi. trong mỗi vị trí của điện cực kích có một loạt các phép đo khác nhau

Ưu điểm:

-Chính xác hơn phương pháp lân cận Nhược điểm

-Phép đo phải thực hiện nhiều hơn

-Dòng kích phải di chuyển nhiều lần

Phương pháp đối lập (Opposite Method): Điện cực kích lần lượt trên các cặp điểm đối xứng

Ưu điểm:

Phân bố dòng đểu hơn nên độ nhạy của phép đo là tốt hơn

Nhược điểm:

-Dòng kích phải thay đổi vị trí

-Vị trí của các cặp điện cực được cho là đối xứng cũng chỉ là tương đối và phụ thuộc vào người thực hiện

Phương pháp thích ứng (Adaptive Method): Điện cực được kích vào tất cả các điểm cần đo

Ưu điểm:

-Phân bố dòng điện là đều nên độ nhạy của phép đo được cải thiện

Nhược điểm:

-Dùng quá nhiều điện cực kích dòng nên số nguồn dòng sử dụng là rất nhiều

Sau khi đã thảo luận trong nhóm quyết định sử dụng Phương pháp lân cận (Neighboring Method) được trình bày dưới đây:

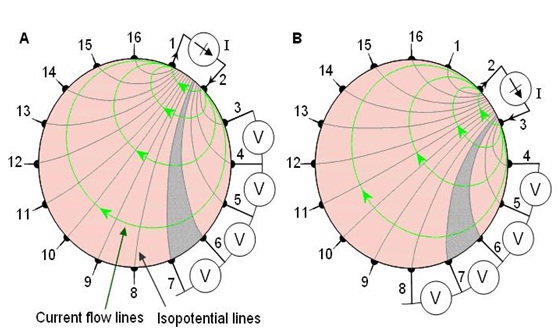

Brown và Segar (1987) đã đề xuất một phương pháp mà dòng được đưa vào qua các điện cực lân cận và điện áp được đo liên tiếp từ tất cả các cặp điện cực liền kề khác. Hình 1 minh họa việc ứng dụng của phương pháp này cho một vật dẫn khối hình trụ với 16 điện cực đặt cách đều nhau.

Dòng được đầu tiên đưa vào qua điện cực 1 và 2 (hình 1A). Mật độ dòng là cao nhất giữa các điện cực này, giảm nhanh chóng như là hàm số của khoảng cách. Điện áp được đo đều đặn liên tục giữa các cặp điện cực 3-4, 4-5, … 15-16. Bốn phép đo đầu tiên trong 13 phép đo được minh họa trong hình 1A. Tất cả 13 phép đo là độc lập. Mỗi trong số chúng được giả định để miêu tả trở kháng giữa phép đo những điện cực dòng đẳng thế giao nhau. Điều này cho biết sự hơi khác nhau của phép đo điện áp giữa điện cực 6 và 7.

(Nghiên cứu sau của Kauppinen, Hyttinen, và Malmivuo (2006) đã chỉ ra rằng những giả định này là không đúng). Sự thiết lập tiếp theo của 13 phép đo điện áp thu được bởi cung cấp dòng qua điện cực 2 và 3, như đã thể hiện trong hình 1B.

Đối với hệ thống 16 điện cực, sẽ thu được 16x13=208 phép đo điện áp. Do có sự qua lại, dòng và áp những điện cực trong những phép đo đó được trao đổi mang lại những kết quả khác nhau. Vì vậy, chỉ có 104 phép đo độc lập. Trong phương pháp lân cận, điện áp thu được là lớn nhất với những cặp điện cực liền kề. Với những cặp điện cực đối diện, điện áp chỉ khoảng 2.5%.

Hình 1: Phương pháp lân cận của dữ liệu trở kháng thu được được minh họa bởi một vật dẫn hình trụ và 16 điện cực đặt cách đều nhau.

(A) Bốn phép đo điện áp đầu tiên trong sự thiết lập 13 phép đo

(B) Sự thiết lập khác của 13 phép đo thu được bởi thay đổi dòng cung cấp cho các điện cực

Phần III.Thiết kế hệ thống thu thập tín hiệu

3.1.Phân tích và sơ đồ khối hệ thống.

a. Phân tích hệ thống

Từ lý thuyêt phương pháp đo trên ta thấy rằng hệ thống phải bao gồm có:

-Nguồn dòng cung cấp dòng xoay chiều I kích vào cơ thể cần có cường độ dòng nhỏ không gây ảnh hưởng tới cơ thể

-Mạch đo điện áp trên các điện cực.

-Thu thập tín hiệu biến đổi số hoá đẩy vào máy tính để phục vụ xử lý tiếp theo.

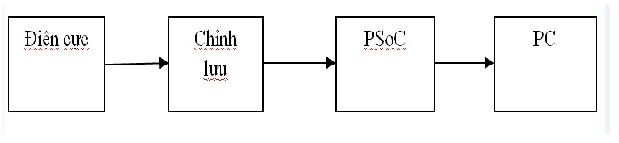

b. Sơ đồ khối tổng quát của hệ thống.

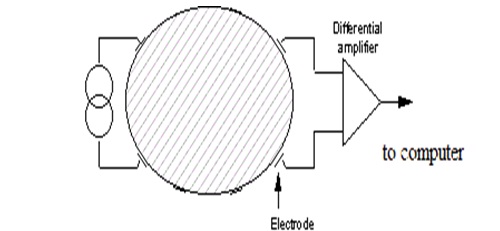

Từ những phân tích trên chúng em đưa ra được sơ đồ khối tổng quát của hệ thống:

Hình 2: Sơ đồ khối tổng quát của hệ thống

3.2.Thiết kế các khối chức năng.

a.Nguồn dòng.

Hình 3.Nguồn dòng

Phân

tích

mạch:

Ta có

U2= Ur/2

U2=U1

Suy ra

U1=Ur/2

Ta lại có

I1= (E0- U1)/R1

I2= (U1-Ur)/R4

I0=(U1-0)/R5

Và I1=I2+I0 Suy ra

(E0-U1)/R1= (U1-Ur)/R4 +U1/R5

Chọn R1=R4 khi đó E0/R1=I0

Chọn E0=9V,f=50Hz,R1=R2=R3=R4=10k

Suy ra I0=0.63 mA.

Với dòng điện 0.63mA không gây ảnh hưởng tới con người

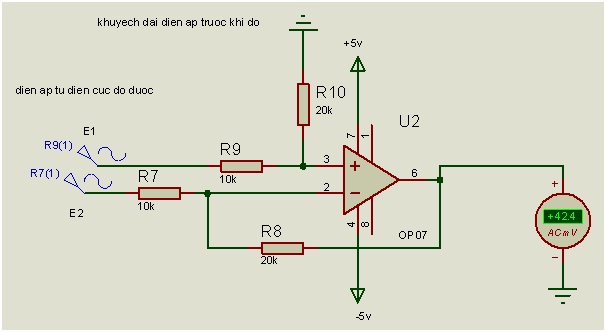

b.Khuyếch đại vi sai.

Hình 4.Khuyếch đại vi sai

Phân tích:

Ta có : Ur1=E1(R10/(R9+R10))( R8/R7+1)

Ur2=E2(-R8/R7)

Ur=Ur1+Ur2

Chọn R10=R8,R9=R7

ta có :

Ur= R8/R7(E1-E2).

Chọn thông số mạch như sau:

R7=10K,R8=20K. Ur= 2(E1-E2)

c. Đưa kết quả thu được vào máy tính phục vụ xử lý tiếp theo.

Sơ đồ khối tổng quát của của khối thu nhận kết quả và hiển thị lên máy tính

-Điện cực: Điện cực được sử dụng có thể là điện cực điện tim hoặc điện cực đồng

-Chỉnh lưu: Do điện áp đo được là điện áp xoay chiều nên phải dùng chỉnh lưu để biến đổi thành điện áp một chiều. Loại chỉnh lưu được sử dụng là chỉnh lưu cầu.

-PSoC (Programable System on Chip): là một thiết bị của Cypress với một ‘hệ thống’ được tích hợp trên một chip và có thể ‘cấu hình’ được phần cứng tùy theo từng ứng dụng.

Sau đây là một vài đặc điểm của PSoC:

.Các chíp PSoC cho phép thay đổi đuợc cấu hình đơn giản bằng cách gán chức năng cho các khối tài nguyên có sẵn trên chíp. Hơn nữa nó còn có thể kết nối tuơng đối mềm dẻo các khối chức năng với nhau hoặc giữa các khối chức năng với các cổng vào ra. Chính vì vậy mà PSoC có thể thay thế cho rất nhiều chức năng nền của một số hệ thống cơ bản chỉ bằng một đơn chíp. Thành phần của chíp PSoC bao gồm các khối ngoại vi số và tuơng tự có thể cấu hình được, một bộ vi xử lý 8 bit, bộ nhớ chương trình (EEROM) có thể lập trình được và bộ nhớ RAM khá lớn.. Việc lập cấu hình cho chíp như thế nào là tùy thuộc vào người lập trình thông qua một số thư viện chuẩn. Người lập trình thiết lập cấu hình trên chíp chỉ đơn giản bằng cách muốn chíp có những chức năng gì thi kéo chức năng đó và thả vào khối tài nguyên số hoặc tương tự, hoặc cả hai tùy theo từng chức năng (Phương pháp lập trình kéo thả). Việc thiết lập ngắt trên chân nào, loại ngắt là gì, các chân vào ra được hoạt động ở chế độ như thế nào đều tùy thuộc vào việc thiết lập của người lập trình khi thiết kế và lập trình cho PSoC. Với khả năng đặt cấu hình mạnh mẽ này, một thiết bị điều khiển, đo lường có thể được gói gọn trên một chip duy nhất. Chính vì lý do đó, hãng Cypress MicroSystems đã không gọi sản phẩm của mình là vi điều khiển (μC) như truyền thống, mà gọi là “thiết bị PSoC” (PSoC device), và họ hy vọng rằng, với khả năng đặt cấu hình mạnh mẽ, người sử dụng sẽ có được những thiết bị điều khiển, những thiết bị đo có giá rẻ, kích thước nhỏ gọn, và sản phẩm PSoC của họ sẽ thay thế được các thiết bị dựa trên vi xử lý hoặc vi điều khiển đã có từ trước đến nay.

Cypress cung cấp các dòng PSoC như CY7C60xxx, CY8C20xxx, CY8C27xxx, CY8C29xxx…

PSoC được sử dụng trong mạch này là CY8C27443.

Với chip CY8C27443 này thì có thể cung cấp các modul sau:

Bộ vi xử lý với cấu trúc Harvard.

Bộ vi xử lý với cấu trúc Harvard.

Tốc độ của bộ vi xử lý lên đến 24 MHz

Lệnh nhân 8 bit x 8 bit, thanh ghi tích lũy là 32 bit

Hoạt động ở tốc độ cao mà năng lượng tiêu hao ít

Dải điện áp hoạt động từ 3.0 tới 5.25V

Điện áp hoạt động có thể giảm xuống 1.0 V sử dụng chế độ kích điện áp

Hoạt động trong dải nhiệt độ từ 400C đến 850C.

12 khối ngoại vi tương tự có thể được thiết lập để làm các nhiệm vụ:

Các bộ ADC lên tới 14 bit

Các bộ DAC lên tới 9 bit.

Các bộ khuếch đại có thể lập trình được hệ số khuếch đại.

Các bộ lọc và các bộ so sánh có thể lập trình được

8 khối ngoại vi số có thể được thiết lập để làm các nhiệm vụ:

Các bộ định thời đa chức năng, đếm sự kiện, đồng hồ thời gian thực, bộ điều chế độ rộng xung có và không có dải an toàn (deadband)

Các modun kiểm tra lỗi (CRC modunles)

Hai bộ truyền thông nối tiếp không đồng bộ hai chiều, hiện nay Cypresss đã cho ra đời loại Psoc hỗ trợ chuẩn USB và USB không dây

Các bộ truyền thông SPI Master hoặc Slave có thể cấu hình được Có thể kết nối với tất cả các chân vào ra.

Bộ nhớ linh hoạt trên chip

Không gian bộ nhớ chương trình Flash từ 4K đến 16K, phụ thuộc vào từng loại chíp với chu kỳ ghi xóa cho bộ nhớ Flash là 50.000 lần

Không gian bộ nhớ RAM là 256 byte

Chíp có thể lập trình thông qua chuẩn nối tiếp (ISSP)

Bộ nhớ Flash có thể được nâng cấp từng phần

Chế độ bảo mật đa năng, tin cậy

Có thể tạo được không gian bộ nhớ Flash trên chíp lên tới 2,304 byte

Có thể lập trình được cấu hình cho từng chân của chip

Các chân vào ra ba trạng thái sử dụng Trigger Schmitt

Đầu ra logic có thể cung cấp dòng 25mA với điện trở treo cao hoặc thấp bên trong

Thay đổi được ngắt trên từng chân

Đường ra tương tự có thể cung cấp dòng tới 40mA

Đường ra đa chức năng có từ 6 đến 44 tùy thuộc vào từng loại chip

Xung nhịp của chíp có thể lập trình được

Bộ tạo dao động 24/48MHz ở bên trong (độ chính xác là 2,5%, không cần thiết bị ngoài)

Có thể lựa chọn bộ dao động ngoài lên tới 24MHz

Bộ dao động thạch anh 32,768 kHz bên trong

Bộ tạo dao động tốc độ thấp bên trong sử dụng cho Watchdog và Sleep

Ngoại vi được thiết lập sẵn

Bộ định thời Watchdog và Sleep phục vụ chế độ an toàn và chế độ nghỉ

Module truyền thông I2C Master và I2C Slave tốc độ lên tới 400kHz

Module phát hiện điện áp thấp được cấu hình bởi người sử dụng

-PC: PSoC được kết nối với PC qua giao tiếp cổng COM với giao diên được lập trình bằng C#

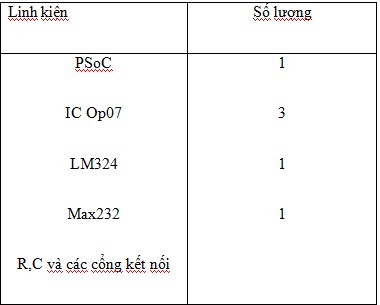

Phụ

lục:

Các

linh

kiện

cần

dùng

DOWNLOAD HERE: Tập tin:Cltk.rar